昭通大關 家庭微工廠解鎖增收密碼

在昭通市大關縣的鄉村,一種創新的‘家庭微工廠’模式正在悄然興起,成為當地群眾實現增收致富的重要途徑。這些微工廠以家庭為單位,通過靈活的生產方式和現代化的管理理念,將傳統手工藝與現代市場需求相結合,不僅帶動了就業,還激活了鄉村經濟的活力。

家庭微工廠主要涵蓋農產品加工、手工藝品制作、特色食品生產等多個領域。例如,一些村民利用自家院落設立小型加工坊,將當地的核桃、竹筍等農產品進行深加工,制作成核桃油、竹筍干等高附加值產品。這些產品通過電商平臺和線下渠道銷往全國各地,甚至遠銷海外,為家庭帶來了可觀的經濟收入。

與此大關縣政府也積極支持這一模式的發展。通過提供技術培訓、資金補貼和市場對接服務,幫助村民解決生產過程中的難題。許多家庭微工廠還引入了互聯網思維,利用社交媒體和直播帶貨等方式拓展銷路,進一步提升了產品的知名度和競爭力。

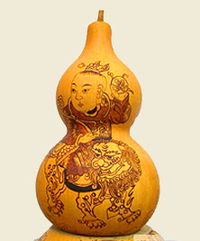

值得一提的是,家庭微工廠不僅促進了經濟增收,還增強了村民的自信心和創造力。許多年輕人選擇返鄉創業,將新穎的設計理念融入傳統工藝中,創作出獨具特色的產品。例如,一些手工藝人將彝族、苗族等民族文化元素與現代時尚結合,設計出受歡迎的服飾和裝飾品,成為市場的新亮點。

昭通大關的‘家庭微工廠’模式為鄉村振興提供了一個可復制的范本。它不僅解鎖了增收密碼,還推動了文化傳承與創新,成為連接傳統與現代的橋梁。隨著更多支持和資源的注入,這一模式有望在更廣范圍內推廣,助力更多家庭實現美好生活。

如若轉載,請注明出處:http://www.hwje.cn/product/35.html

更新時間:2026-03-15 22:49:40